VSC Fault Protection

| Fault In Our System | |

| Team Name | Faults In Our System (FIOS) |

| Duration | Fall 2017 - Spring 2018 |

| Team Member |

|

| Instructor |

|

| Sponsor |

SEL Research & Development |

Voltage Source Converter Fault (VSC) Protection

The objective is to design and test a power system protection scheme that combines voltage and possible measurements from different locations in or near a wind farm to locate faults.

Problem Definition[edit | edit source]

Project Learning[edit | edit source]

Some of the equipment and programs we used:

- Real Time Digital Simulator (RTDS) -- The Real Time Digital Simulator (RTDS) is a special purpose computer that does time domain simulation solving the differential equations for a power system at discrete instants in time, 50 microseconds apart, and doing analog or digital I/O to external protection and control devices in real time. Such that the external devices don't know they are talking to a simulation instead of a real system.

- RSCAD -- A graphical interface intended to be used in conjunction with RTDS.

- PSCAD -- A non-real time graphical interface program that is the forerunner to RSCAD.

Project background[edit | edit source]

Type 3 WTG & Type 4 WTG[edit | edit source]

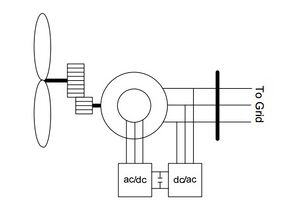

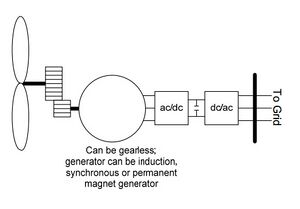

- For the Type 4 Wind Turbine Generator (WTG):

- 1. WTG is either Permanent Magnet Synchronous Machine or Squirrel Cage Induction Machine.

- 2. Connection to AC/AC converter.

- 3. Control system for converter by inner control loop and outer control loop.

- 4. Connection to Delta-to-Wye Transformer to the AC Grid.

Faults[edit | edit source]

- What are Faults?

An electrical fault is an abnormal defect in an electrical system caused by equipment failures, human errors, and/or environmental incidents.

- Types of Faults

There are two main types of faults: symmetrical ones and unsymmetrical ones.

- Symmetrical – a balanced three phase fault

- Three Phase Ground Faults (Line-Line-Line-Ground Fault/LLLG) - 2-5%of the time

- Three Phase Faults (Line-Line-Line Fault/LLL) - 2-5%of the time

- Unsymmetrical – does not affect all three phases

- Line-To-Line Faults (LL) - 5-10% of the time

- Single-Line-To-Ground Faults (SLG) - 65-70% of the time

- Double-Line-Ground Faults (DLG) - 15-20% of the time

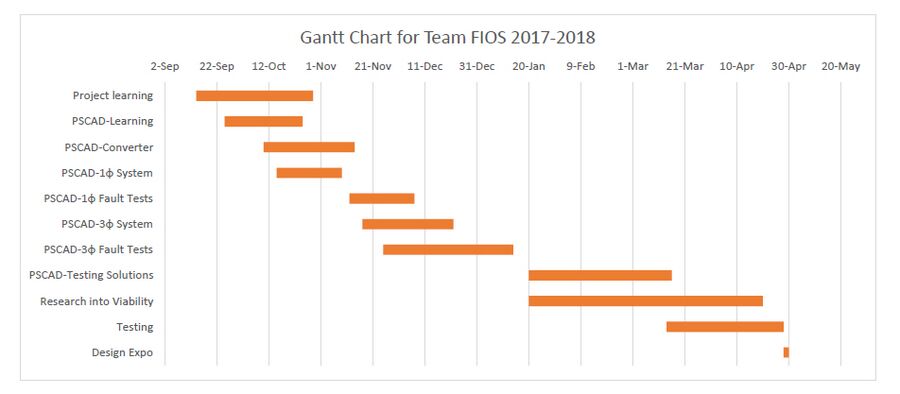

Schedule[edit | edit source]

Gantt Chart[edit | edit source]

Design[edit | edit source]

System Diagrams[edit | edit source]

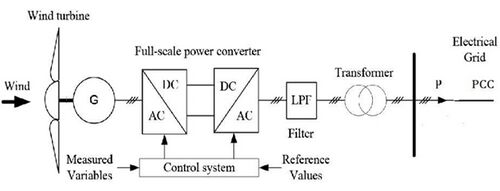

The system diagram of type 4 wind turbine generator (seen above in Figure 3) shows it is providing mechanical power to a permanent magnet synchronous machine (PMSM) as you can see in the Figure 3. This then provides electrical power to a diode bridge rectifier to convert AC to DC. Then the power will flow through a DQ0 link and then convert DC back to AC through the active Pulse-width modulation (PWM) VSC. This output will go through a transformer and then to the AC grid. A squirrel cage induction machine can also be used in place of the PMSM.

Engineering Modeling[edit | edit source]

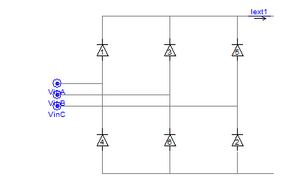

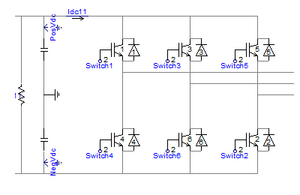

The projects model was built in RTDS for both the diode bridge rectifier (Figure 5) and the two-level converter(Figure 6).

The diode bridge rectifier is used to rectify the AC input from the generator to a DC output. To convert DC back to a source of AC that the power grid can use, the active grid side voltage converter is used.

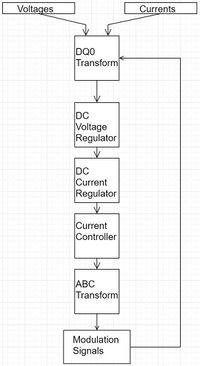

On top of the power electronics models implemented above, a controller was designed, by Shashidhar Reddy Sathu, to generate the modulating functions for the three phase legs based on real and reactive power set points. Below are the outer control loop and inner control loop.

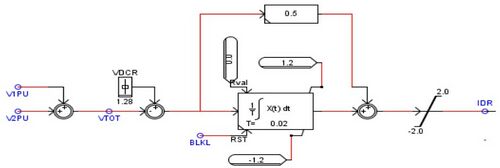

Outer control Loop[edit | edit source]

The outer control loop was created for determining Id and Iq reference values from the set point values for real and reactive power. In the case of a wind turbine, the output power from the generator is hard to determine correctly and the Id reference value needs to follow the generator output, otherwise the energy gets dumped into the capacitor and raises the DC bus voltage and could damage the power electronic devices. In another case, if the power input falls and the inverter supplies more AC power than is coming into the DC link, the voltage will fall as the capacitor gets drained and the system will not be able to maintain the voltage at the inverter terminals. This control loop was implemented to vary the exported ac power with the change in input and is based on regulating the DC link voltage.

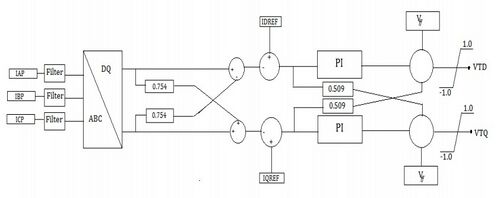

Inner control Loop[edit | edit source]

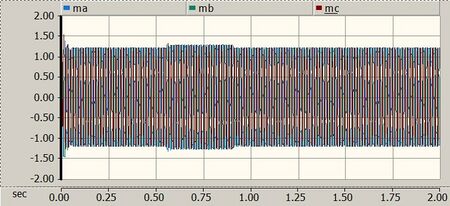

The inner control loop generates modulating waves for all three phases for the use in switching functions. The Id and Iq reference values are compared with the processed measured values. The controller determines the voltage that has to be supplied to the terminals to drive the current corresponding to the reference values. The control is done in the synchronous dq0 reference frame and has to be transformed back into the ABC reference frame to generate the modulating waves for the three phases.

PSCAD Design[edit | edit source]

- Three Phase Simulation

| Comment | Diagram |

|---|---|

After the single phase fault model built, we start to build the three phase model. Briefly, we add a transformer inside of our circuit, and we try to use the feedback loop, the state base model in the terminal side to gain a more stable system. |

|

For the control flow in our project, we will do the following processing of the signal:

After all these processes, we could get the modulation signal. |

Result[edit | edit source]

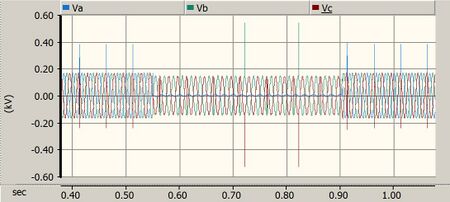

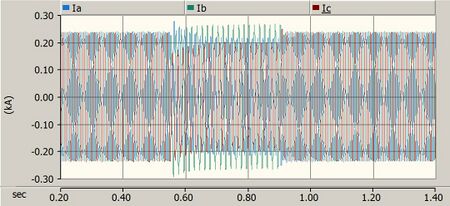

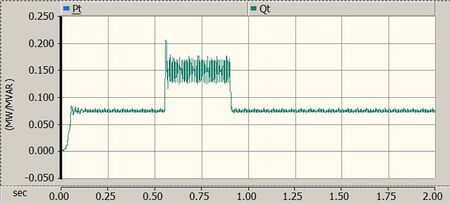

After modelling, here, we initiate a Single-Line-Ground (SLG) fault waveform as an example.

And we set the fault occurence bounds at 0.55 and 0.9 on the time scale.

Normally, when a fault occurs, the voltage drops and the current will go up to an infinite amount can damage the system. However, thanks to the control system, we are able to regulate this current through the system. As seen in the simulations above, we are able to detect a fault using the voltage depressions, but the current, although changing slightly, is able to ride the fault with a similar current value.

Deign Summary[edit | edit source]

Through our project, we implement a type 4 WTG in PSCAD and utilize the terminal and source voltage depressions as information to determine a fault type and phase while regulating the source current to the grid. To do this we modulated the signal by converting the three-phase system to a two-axis system (DQ0). To explore numerous fault possibilities, we created this system in both the stationary and the synchronous reference frames. Moving to the stationary reference frame we used the Clarke's transform and a control diagram found in Voltage-Sourced Converters' textbook. A similar procedure for the synchronous frame was used, except we used Park's transform. By doing this we were able to see the effects of a fault in the system and determined that we can use set points on time stamped PMU (Phasor Measurement Unit) to locate the fault.

Future steps[edit | edit source]

- Test ideas in RTDS lab.

- Transmission implementation with low impedance fault.

- Future research with untransposed lines and high fault impedance.

- Economic analysis of implementation of PMUs or another type of data collection with node to node communication.

Team Information[edit | edit source]

| Team members listed below from left to right |

|---|

Document Archive[edit | edit source]

Weekly Meeting Minutes[edit | edit source]

Fall Semester[edit | edit source]

File:Minutes from 9 14 2017.pdf

File:Minutes from 9 28 2017.pdf

File:Minutes from 10 3 2017.pdf

File:Minutes from 10 10 2017.pdf

File:Minutes from 10 17 2017.pdf

File:Minutes from 10 24 2017.pdf

File:Minutes from 10 31 2017.pdf

File:Minutes from 11 7 2018.pdf

File:Minutes from 11 28 2018.pdf

Spring Semester[edit | edit source]

File:Minutes from 1 19 2018.pdf

File:Minutes from 1 26 2018.pdf

File:Minutes from 2 2 2018.pdf

File:Minutes from 2 16 2018.pdf

File:Minutes from 2 23 2018.pdf

File:Minutes from 3 2 2018.pdf

File:Minutes from 3 23 2018.pdf

File:Minutes from 4 6 2018.pdf

Project Documents[edit | edit source]

File:Team Contract.pdf

File:SEL Client Transcript.pdf

File:Gantt Chart FIOS.pdf

File:Expo Board FIOS.pdf